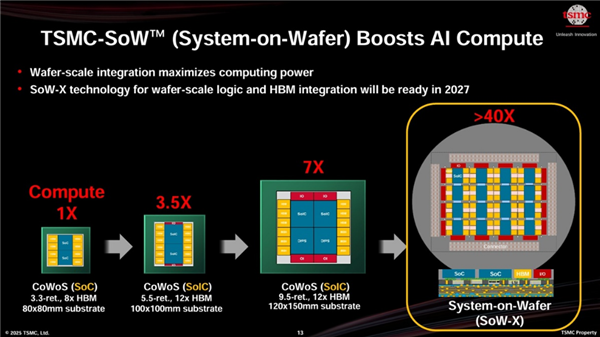

本站6月12日消息,據媒體報道,臺積電正積極籌備新一代 CoPoS(Chip-on-Panel-on-Substrate) 封裝技術,該技術能將封裝基板尺寸顯著擴展至310 x 310mm甚至更大。

CoPoS的核心創新在于將中介層“面板化”,這是對現有CoWoS-L和CoWoS-R(基于方形基板)的進一步演進。其本質是用大型矩形面板基板替代了傳統的圓形晶圓作為載體。

根據規劃,臺積電將于2026年建立CoPoS試點生產線,2027年重點進行工藝優化以滿足合作伙伴需求,目標在2028年底至2029年初實現CoPoS量產。

與FOPLP(扇出型面板級封裝)一樣,CoPoS(基板上面板芯片封裝)也采用大型面板基板進行封裝,不過兩者存在一些差異。FOPLP是一種不需要中介層的封裝方法,芯片直接重新分布在面板基板上,并通過重分布層(RDL)互連。

這種方法具有成本低、I/O密度高、外形尺寸靈活等優勢,適用于邊緣AI、移動設備和集成密度適中的中端ASIC等應用。

CoPoS則引入了中介層,從而有著更高的信號完整性和穩定的功率傳輸,對于集成GPU和HBM芯片的高端產品來說效果更好。同時中介層材料正從傳統的硅變為玻璃,將提供更高的成本效益和熱穩定性。預計未來CoPoS將取代CoWoS-L,而英偉達很可能會是首個合作伙伴。

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播更多信息之目的,如作者信息標記有誤,請第一時間聯系我們修改或刪除,多謝。